ARTIX-7 FPGA

ዋና ቦርድ

AC7A200

በሞጁል ላይ ስርዓት

የተጠቃሚ መመሪያ

የስሪት መዝገብ

| ሥሪት | ቀን | መልቀቅ በ | መግለጫ |

| ራዕ 1.0 | 28-06-20 | ራቸል ዡ | የመጀመሪያ ልቀት |

ክፍል 1: AC7A200 ኮር ቦርድ መግቢያ

AC7A200 (ኮር ቦርድ ሞዴል, ከታች ተመሳሳይ) FPGA ኮር ቦርድ, በ XILINX's ARTIX-7 ተከታታይ 100T XC7A200T-2FBG484I ላይ የተመሰረተ ነው. ከፍተኛ ፍጥነት, ከፍተኛ የመተላለፊያ ይዘት እና ከፍተኛ አቅም ያለው ከፍተኛ አፈጻጸም ያለው ኮር ቦርድ ነው. ለከፍተኛ ፍጥነት የውሂብ ግንኙነት, የቪዲዮ ምስል ማቀናበር, ከፍተኛ ፍጥነት ያለው መረጃ ለማግኘት ወዘተ ተስማሚ ነው.

ይህ AC7A200 ኮር ቦርድ ሁለት የ MICRON MT41J256M16HA-125 DDR3 ቺፕ ይጠቀማል እያንዳንዱ DDR 4Gbit አቅም አለው; ሁለት DDR ቺፖችን ወደ 32-ቢት ዳታ አውቶቡስ ስፋት ይጣመራሉ እና በ FPGA እና DDR3 መካከል ያለው የማንበብ/የመፃፍ የውሂብ መተላለፊያ ይዘት እስከ 25Gb; እንዲህ ዓይነቱ ውቅር ከፍተኛ የመተላለፊያ ይዘት ውሂብ ሂደት ፍላጎቶችን ሊያሟላ ይችላል.

የAC7A200 ኮር ቦርድ 180 መደበኛ IO ወደቦች የ3.3V ደረጃ፣ 15 መደበኛ IO ወደቦች 1.5V ደረጃ እና 4 ጥንድ የጂቲፒ ከፍተኛ ፍጥነት RX/TX ልዩነት ምልክቶችን ያሰፋል። ብዙ አይኦ ለሚያስፈልጋቸው ተጠቃሚዎች ይህ ኮር ቦርድ ጥሩ ምርጫ ይሆናል። ከዚህም በላይ በ FPGA ቺፕ እና በይነገጽ መካከል ያለው መስመር እኩል ርዝመት እና ልዩነት ማቀነባበሪያ ነው, እና የኮር ቦርድ መጠን 2.36 ኢንች * 2.36 ኢንች ብቻ ነው, ይህም ለሁለተኛ ደረጃ እድገት በጣም ተስማሚ ነው.

ምስል 1-1፡ AC7A200 ኮር ቦርድ (የፊት View)

ምስል 1-2፡ AC7A200 ኮር ቦርድ (የኋላ View)

ክፍል 2: FPGA ቺፕ

ከላይ እንደተጠቀሰው፣ የምንጠቀመው የFPGA ሞዴል XC7A200T-2FBG484I ነው፣ እሱም የ Xilinx's Artix-7 ተከታታይ ነው። የፍጥነት ደረጃው 2 ነው፣ እና የሙቀት ደረጃው የኢንዱስትሪ ደረጃ ነው። ይህ ሞዴል 484 ፒን ያለው የFGG484 ጥቅል ነው። Xilinx ARTIX-7 FPGA ቺፕ መሰየምን ህጎች ከዚህ በታች

ምስል 2-1: የ ARTIX-7 ተከታታይ ልዩ ቺፕ ሞዴል ፍቺ

ምስል 2-2: በቦርዱ ላይ የ FPGA ቺፕ

የ FPGA ቺፕ XC7A200T ዋና መለኪያዎች እንደሚከተለው ናቸው

| ስም | የተወሰኑ መለኪያዎች |

| የሎጂክ ሴሎች | 215360 |

| ቁርጥራጮች | 16-02-92 |

| CLB ይግለጡ-flops | 269200 |

| RAM (kb) አግድ | 13140 |

| DSP ቁርጥራጮች | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC፣ 12bit፣ 1Mbps AD |

| ጂቲፒ አስተላላፊ | 4 GTP፣ 6.6Gb/s ቢበዛ |

| የፍጥነት ደረጃ | -2 |

| የሙቀት ደረጃ | የኢንዱስትሪ |

የ FPGA የኃይል አቅርቦት ስርዓት

Artix-7 FPGA የኃይል አቅርቦቶች VCCINT፣ VCCBRAM፣ VCCAUX፣ VCCO፣ VMGTAVCC እና VMGTAVTT ናቸው። VCCINT ከ 1.0 ቪ ጋር መገናኘት የሚያስፈልገው የ FPGA ኮር የኃይል አቅርቦት ፒን ነው; VCCBRAM የ FPGA የኃይል አቅርቦት ፒን ነው አግድ RAM, ከ 1.0 ቪ ጋር ይገናኙ; VCCAUX የ FPGA ረዳት የኃይል አቅርቦት ፒን ነው, 1.8V ያገናኙ; ቪሲኮ ጥራዝ ነው።tagሠ የእያንዳንዱ የ FPGA ባንክ፣ BANK0፣ BANK13~16፣ BANK34~35 ጨምሮ። በ AC7A200 FPGA ኮር ቦርድ ላይ BANK34 እና BANK35 ከ DDR3 ጋር መገናኘት አለባቸውtagየባንኩ ኢ ግንኙነት 1.5 ቪ ነው, እና ጥራዝtagኢ የሌላ ባንክ 3.3 ቪ ነው። የBANK15 እና BANK16 ቪሲኮ በኤልዲኦ የተጎላበተ ሲሆን የኤልዲኦ ቺፕን በመተካት ሊቀየር ይችላል። VMGTAVCC የአቅርቦት ጥራዝ ነውtagከ 1.0 ቪ ጋር የተገናኘ የ FPGA ውስጣዊ ጂቲፒ አስተላላፊ; VMGTAVTT የማቋረጫ ጥራዝ ነው።tagሠ የ GTP ትራንሴቨር፣ ከ 1.2 ቪ ጋር የተገናኘ።

የአርቲክስ-7 FPGA ስርዓት የኃይል አወጣጥ ቅደም ተከተል በ VCCINT፣ ከዚያም VCCBRAM፣ ከዚያም VCCAUX እና በመጨረሻም VCCO ሃይል እንዲሆን ይጠይቃል። VCCINT እና VCCBRAM ተመሳሳይ ጥራዝ ካላቸውtagሠ፣ በአንድ ጊዜ ሊሞሉ ይችላሉ። የኃይል ቅደም ተከተል እርስዎtages ተገልብጧል። የጂቲፒ ትራንስሴቨር የኃይል አወጣጥ ቅደም ተከተል VCCINT፣ ከዚያ VMGTAVCC፣ ከዚያ VMGTAVTT ነው። VCCINT እና VMGTAVCC ተመሳሳይ ጥራዝ ካላቸውtagሠ፣ በአንድ ጊዜ ሊሞሉ ይችላሉ። የኃይል ማጥፋት ቅደም ተከተል ከኃይል-ተኮር ቅደም ተከተል ተቃራኒ ነው.

ክፍል 3: ንቁ ልዩነት ክሪስታል

የ AC7A200 ኮር ቦርድ ሁለት ሲታይም ንቁ ልዩነት ክሪስታሎች የታጠቁ ነው, አንድ 200MHz ነው, ሞዴሉ SiT9102-200.00MHz ነው, የስርዓት ዋና ሰዓት FPGA እና DDR3 መቆጣጠሪያ ሰዓት ለማመንጨት; ሌላው 125 ሜኸ ነው፣ ሞዴሉ SiT9102 -125MHz ነው፣ የማጣቀሻ ሰዓት ግብአት ለጂቲፒ transceivers።

ክፍል 3.1: 200Mhz ንቁ ልዩነት ሰዓት

G1 በስእል 3-1 የ 200M ገባሪ ልዩነት ክሪስታል ሲሆን ይህም የእድገት ቦርድ ስርዓት የሰዓት ምንጭን ያቀርባል. የክሪስታል ውፅዓት ከ FPGA BANK34 አለምአቀፍ የሰዓት ፒን MRCC (R4 እና T4) ጋር ተገናኝቷል። ይህ 200Mhz ልዩነት ሰዓት የተጠቃሚውን አመክንዮ በ FPGA ውስጥ ለመንዳት ሊያገለግል ይችላል። ተጠቃሚዎች የተለያዩ ድግግሞሾችን ለማመንጨት PLLs እና DCMsን በFPGA ውስጥ ማዋቀር ይችላሉ።

ምስል 3-1: 200Mhz ንቁ ልዩነት ክሪስታል ሼሜቲክ

ምስል 3-2፡ 200Mhz ገባሪ ልዩነት ክሪስታል በኮር ቦርድ ላይ

200Mhz ልዩነት የሰዓት ፒን ምደባ

| የምልክት ስም | FPGA ፒን |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

ክፍል 3.2: 125 ሜኸ ንቁ ልዩነት ክሪስታል

በስእል 2-3 ላይ ያለው G3 125ሜኸ ንቁ ልዩነት ክሪስታል ነው፣ እሱም በFPGA ውስጥ ላለው የጂቲፒ ሞጁል የቀረበው የማጣቀሻ ግብዓት ሰዓት ነው። የክሪስታል ውፅዓት ከጂቲፒ BANK216 የሰዓት ፒን MGTREFCLK0P (F6) እና MGTREFCLK0N (E6) የFPGA ጋር ተገናኝቷል።

ምስል 3-3፡ 125ሜኸ ንቁ ልዩነት ክሪስታል ሼማቲክ

ምስል 3-4፡ 125 ሜኸ ንቁ ልዩነት ክሪስታል በኮር ቦርድ ላይ

125 ሜኸ ልዩነት የሰዓት ፒን ምደባ

| የተጣራ ስም | FPGA ፒን |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

ክፍል 4: DDR3 DRAM

የ FPGA ኮር ቦርድ AC7A200 ባለሁለት ማይክሮን 4ጂቢት (512ሜባ) DDR3 ቺፖችን (በአጠቃላይ 8ጂቢት)፣ ሞዴል MT41J256M16HA-125 ነው (ከMT41K256M16HA-125 ጋር ተኳሃኝ)። የ DDR3 SDRAM ከፍተኛው የስራ ፍጥነት 400ሜኸ (የመረጃ መጠን 800Mbps) አለው። የ DDR3 ማህደረ ትውስታ ስርዓት በቀጥታ ከ FPGA BANK 34 እና BANK35 ማህደረ ትውስታ በይነገጽ ጋር የተገናኘ ነው. የ DDR3 SDRAM የተወሰነ ውቅር በሰንጠረዥ 4-1 ላይ ይታያል።

| ቢት ቁጥር | ቺፕ ሞዴል | አቅም | ፋብሪካ |

| U5,U6 | MT41J256M16HA-125 | 256M x 16 ቢት | ማይክሮን |

ሠንጠረዥ 4-1: DDR3 SDRAM ውቅር

የ DDR3 ሃርድዌር ዲዛይን የሲግናል ታማኝነት ጥብቅ ግምት ያስፈልገዋል። የ DDR3 ከፍተኛ ፍጥነት እና የተረጋጋ አሠራር ለማረጋገጥ በሴክዩት ዲዛይን እና በፒሲቢ ዲዛይን ውስጥ የሚዛመደውን ተከላካይ/ተርሚናል የመቋቋም፣ የክትትል እክል መቆጣጠሪያ እና የርዝመት መቆጣጠሪያን ሙሉ በሙሉ ተመልክተናል። ምስል 4-1 የ DDR3 DRAM ሃርድዌር ግንኙነትን ይዘረዝራል።

ምስል 4-1፡ የ DDR3 DRAM Schematic

ምስል 4-2፡ በኮር ቦርድ ላይ ያለው DDR3

የ DDR3 DRAM ፒን ምደባ፡-

| የተጣራ ስም | የ FPGA ፒን ስም | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | አአ4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | አአ5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | አአ3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | አአ1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_ዳግም አስጀምር | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

ክፍል 5: QSPI ፍላሽ

የ FPGA ኮር ቦርድ AC7A200 አንድ ባለ 128Mbit QSPI FLASH የተገጠመለት ሲሆን ሞዴሉ N25Q128 ነው 3.3V CMOS voltagሠ መደበኛ. በ QSPI FLASH ተለዋዋጭነት ተፈጥሮ ምክንያት የስርዓቱን የማስነሻ ምስል ለማከማቸት እንደ ማስነሻ መሳሪያ ሆኖ ሊያገለግል ይችላል። እነዚህ ምስሎች በዋናነት FPGA ቢትን ያካትታሉ files፣ የ ARM መተግበሪያ ኮድ፣ የለስላሳ ኮር መተግበሪያ ኮድ እና ሌላ የተጠቃሚ ውሂብ fileኤስ. የ SPI FLASH ልዩ ሞዴሎች እና ተዛማጅ መለኪያዎች በሰንጠረዥ 5-1 ውስጥ ይታያሉ።

| አቀማመጥ | ሞዴል | አቅም | ፋብሪካ |

| U8 | N25Q128 | 128M ቢት | ኑሞኒክስ |

ሠንጠረዥ 5-1፡ QSPI FLASH መግለጫ

QSPI FLASH ከተወሰኑት የ BANK0 እና BANK14 የFPGA ቺፕ ፒን ጋር ተገናኝቷል። የሰዓት ፒን ከ BANK0 CCLK0 ጋር የተገናኘ ሲሆን ሌሎች ዳታ እና ቺፕ ምረጥ ሲግናሎች ከ D00~D03 እና FCS የ BANK14 ፒን ጋር ተያይዘዋል። ምስል 5-1 የQSPI ፍላሽ ሃርድዌር ግንኙነትን ያሳያል።

ምስል 5-1፡ QSPI Flash Schematic

የQSPI ፍላሽ ፒን ምደባዎች፡-

| የተጣራ ስም | የ FPGA ፒን ስም | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

ምስል 5-2፡ QSPI FLASH በኮር ቦርድ ላይ

ክፍል 6: በኮር ቦርድ ላይ የ LED መብራት

በ AC3A7 FPGA ኮር ቦርድ ላይ 200 ቀይ የ LED መብራቶች አሉ ከነዚህም አንዱ የኃይል አመልካች መብራት (PWR) ነው፣ አንደኛው የውቅር LED መብራት (ተከናውኗል) እና አንዱ የተጠቃሚው የ LED መብራት ነው። የኮር ቦርዱ ሲሰራ, የኃይል አመልካች ያበራል; FPGA ሲዋቀር የ LED ውቅር ያበራል። የተጠቃሚው የ LED መብራት ከ BANK34 IO ጋር ተገናኝቷል, ተጠቃሚው መብራቱን በፕሮግራሙ መቆጣጠር ይችላል. መቼ አይኦ ጥራዝtagሠ ከተጠቃሚው ጋር የተገናኘ LED ከፍተኛ ነው, የተጠቃሚው LED ያበራል. መቼ ግንኙነት IO voltage ዝቅተኛ ነው, የተጠቃሚው LED ይጠፋል. የ LED ብርሃን ሃርድዌር ግንኙነት ንድፍ ንድፍ በስእል 6-1 ይታያል።

ምስል 6-1: በኮር ቦርዱ ንድፍ ላይ የ LED መብራቶች

ምስል 6-2: በኮር ቦርድ ላይ የ LED መብራቶች

የተጠቃሚ LEDs ፒን ምደባ

| የምልክት ስም | የ FPGA ፒን ስም | FPGA ፒን ቁጥር | መግለጫ |

| LED1 | IO_L15N_T2_DQS_34 | W5 | የተጠቃሚ LED |

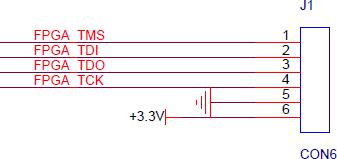

ክፍል 7፡ ጄTAG በይነገጽ

ጄTAG የሙከራ ሶኬት J1 በ AC7A200 ኮር ሰሌዳ ላይ ለጄ ተይዟልTAG የኮር ቦርዱ ብቻውን ጥቅም ላይ ሲውል ማውረድ እና ማረም. ምስል 7-1 የጄTAG ወደብ, ይህም TMS, TDI, TDO, TCK ያካትታል. , GND, + 3.3V እነዚህ ስድስት ምልክቶች.

ምስል 7-1፡ ጄTAG የበይነገጽ ንድፍ

ጄTAG በይነገጽ J1 በAC7A200 FPGA ኮር ቦርድ ባለ 6-ሚስማር 2.54ሚሜ ፒክ ባለ አንድ ረድፍ የሙከራ ቀዳዳ ይጠቀማል። ጄን መጠቀም ከፈለጉTAG በኮር ቦርዱ ላይ ለማረም ማገናኛ፣ ባለ 6-ሚስማር ባለአንድ ረድፍ ፒን ራስጌ መሸጥ ያስፈልግዎታል።

ምስል 7-2 የጄTAG በይነገጽ J1 በ AC7A200 FPGA ኮር ሰሌዳ ላይ።

ምስል 7-2 ጄTAG በኮር ቦርድ ላይ በይነገጽ

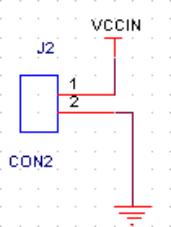

ክፍል 8: በኮር ቦርድ ላይ የኃይል በይነገጽ

የ AC7A200 FPGA ኮር ቦርድ ብቻውን እንዲሰራ ለማድረግ የኮር ቦርዱ ባለ 2-ፒን የኃይል አቅርቦት በይነገጽ J2 የተጠበቀ ነው። ተጠቃሚው የኮር ቦርዱን ተግባር በተናጠል ማረም ከፈለገ (ያለ ተሸካሚ ሰሌዳ) ውጫዊ መሳሪያው ለኮር ቦርዱ ኃይል ለማቅረብ + 5V ማቅረብ ያስፈልገዋል.

ምስል 8-1፡ በኮር ቦርዱ ላይ የሃይል በይነገጽ ንድፍ

ምስል 8-2፡ በኮር ቦርዱ ላይ ያለው የኃይል በይነገጽ

ክፍል 9: ቦርድ ወደ ቦርድ አያያዦች ፒን ምደባ

የኮር ቦርዱ በአጠቃላይ አራት ከፍተኛ ፍጥነት ያለው ቦርድ ወደ ቦርድ ማገናኛዎች አሉት.

የኮር ቦርዱ ከድምጸ ተያያዥ ሞደም ጋር ለመገናኘት አራት ባለ 80-ሚስማር ኢንተር-ቦርድ ማያያዣዎችን ይጠቀማል። የ FPGA አይኦ ወደብ ከአራቱ ማገናኛዎች ጋር በዲፈረንሻል ማዞሪያ ተያይዟል። የማገናኛዎቹ የፒን ክፍተት 0.5 ሚሜ ነው, ለከፍተኛ ፍጥነት የውሂብ ግንኙነት በአገልግሎት አቅራቢው ሰሌዳ ላይ ወደ ቦርድ ማገናኛዎች ያስገቡ.

ቦርድ ወደ ቦርድ አያያዦች CON1

የ 80-pin ቦርድ ወደ ቦርድ ማገናኛዎች CON1, ከ VCCIN ኃይል አቅርቦት (+ 5V) ጋር ለመገናኘት እና በአገልግሎት አቅራቢው ሰሌዳ ላይ ያለው መሬት, የ FPGA መደበኛ አይኦዎችን ያራዝመዋል. እዚህ ላይ ልብ ሊባል የሚገባው 15 የ CON1 ፒን ከ IO ወደብ BANK34 ጋር የተገናኘ ነው, ምክንያቱም የ BANK34 ግንኙነት ከ DDR3 ጋር የተገናኘ ነው. ስለዚህ, ጥራዝtagየዚህ BANK34 የሁሉም አይኦዎች ደረጃ 1.5V ነው።

የቦርድ ምደባ ለቦርድ ማያያዣዎች CON1

| CON1 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

CON1 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

| ፒን 1 | ቪሲሲን | – | + 5 ቪ | ፒን 2 | ቪሲሲን | – | + 5 ቪ |

| ፒን 3 | ቪሲሲን | – | + 5 ቪ | ፒን 4 | ቪሲሲን | – | + 5 ቪ |

| ፒን 5 | ቪሲሲን | – | + 5 ቪ | ፒን 6 | ቪሲሲን | – | + 5 ቪ |

| ፒን 7 | ቪሲሲን | – | + 5 ቪ | ፒን 8 | ቪሲሲን | – | + 5 ቪ |

| ፒን 9 | ጂኤንዲ | – | መሬት | ፒን 10 | ጂኤንዲ | – | መሬት |

| ፒን 11 | NC | – | NC | ፒን 12 | NC | – | NC |

| ፒን 13 | NC | – | NC | ፒን 14 | NC | – | NC |

| ፒን 15 | NC | – | NC | ፒን 16 | B13_L4_P | አአ15 | 3.3 ቪ |

| ፒን 17 | NC | – | NC | ፒን 18 | B13_L4_N | AB15 | 3.3 ቪ |

| ፒን 19 | ጂኤንዲ | – | መሬት | ፒን 20 | ጂኤንዲ | – | መሬት |

| ፒን 21 | B13_L5_P | Y13 | 3.3 ቪ | ፒን 22 | B13_L1_P | Y16 | 3.3 ቪ |

| ፒን 23 | B13_L5_N | አአ14 | 3.3 ቪ | ፒን 24 | B13_L1_N | አአ16 | 3.3 ቪ |

| ፒን 25 | B13_L7_P | AB11 | 3.3 ቪ | ፒን 26 | B13_L2_P | AB16 | 3.3 ቪ |

| ፒን 27 | B13_L7_P | AB12 | 3.3 ቪ | ፒን 28 | B13_L2_N | AB17 | 3.3 ቪ |

| ፒን 29 | ጂኤንዲ | – | መሬት | ፒን 30 | ጂኤንዲ | – | መሬት |

| ፒን 31 | B13_L3_P | አአ13 | 3.3 ቪ | ፒን 32 | B13_L6_P | ወ14 | 3.3 ቪ |

| ፒን 33 | B13_L3_N | AB13 | 3.3 ቪ | ፒን 34 | B13_L6_N | Y14 | 3.3 ቪ |

| ፒን 35 | B34_L23_P | Y8 | 1.5 ቪ | ፒን 36 | B34_L20_P | AB7 | 1.5 ቪ |

| ፒን 37 | B34_L23_N | Y7 | 1.5 ቪ | ፒን 38 | B34_L20_N | AB6 | 1.5 ቪ |

| ፒን 39 | ጂኤንዲ | – | መሬት | ፒን 40 | ጂኤንዲ | – | መሬት |

| ፒን 41 | B34_L18_N | አአ6 | 1.5 ቪ | ፒን 42 | B34_L21_N | V8 | 1.5 ቪ |

| ፒን 43 | B34_L18_P | Y6 | 1.5 ቪ | ፒን 44 | B34_L21_P | V9 | 1.5 ቪ |

| ፒን 45 | B34_L19_P | V7 | 1.5 ቪ | ፒን 46 | B34_L22_P | አአ8 | 1.5 ቪ |

| ፒን 47 | B34_L19_N | W7 | 1.5 ቪ | ፒን 48 | B34_L22_N | AB8 | 1.5 ቪ |

| ፒን 49 | ጂኤንዲ | – | መሬት | ፒን 50 | ጂኤንዲ | – | መሬት |

| ፒን 51 | XADC_VN | M9 | አናሎግ | ፒን 52 | NC | ||

| ፒን 53 | XADC_VP | L10 | አናሎግ | ፒን 54 | B34_L25 | U7 | 1.5 ቪ |

| ፒን 55 | NC | – | NC | ፒን 56 | B34_L24_P | W9 | 1.5 ቪ |

| ፒን 57 | NC | – | NC | ፒን 58 | B34_L24_N | Y9 | 1.5 ቪ |

| ፒን 59 | ጂኤንዲ | – | መሬት | ፒን 60 | ጂኤንዲ | – | መሬት |

| ፒን 61 | B16_L1_N | F14 | 3.3 ቪ | ፒን 62 | NC | – | NC |

| ፒን 63 | B16_L1_P | F13 | 3.3 ቪ | ፒን 64 | NC | – | NC |

| ፒን 65 | B16_L4_N | E14 | 3.3 ቪ | ፒን 66 | NC | – | NC |

| ፒን 67 | B16_L4_P | E13 | 3.3 ቪ | ፒን 68 | NC | – | NC |

| ፒን 69 | ጂኤንዲ | – | መሬት | ፒን 70 | ጂኤንዲ | – | መሬት |

| ፒን 71 | B16_L6_N | ዲ15 | 3.3 ቪ | ፒን 72 | NC | – | NC |

| ፒን 73 | B16_L6_P | ዲ14 | 3.3 ቪ | ፒን 74 | NC | – | NC |

| ፒን 75 | B16_L8_P | C13 | 3.3 ቪ | ፒን 76 | NC | – | NC |

| ፒን 77 | B16_L8_N | ብ13 | 3.3 ቪ | ፒን 78 | NC | – | NC |

| ፒን 79 | NC | – | NC | ፒን 80 | NC | – | NC |

ምስል 9-1፡ ከቦርድ ወደ ቦርድ ማገናኛዎች CON1 በኮር ቦርድ ላይ

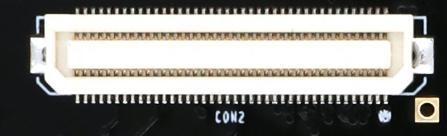

ቦርድ ወደ ቦርድ አያያዦች CON2

ባለ 80-ፒን የሴት ግንኙነት ራስጌ CON2 የ FPGA BANK13 እና BANK14 መደበኛ አይኦ ለማራዘም ይጠቅማል። ጥራዝtagየሁለቱም ባንኮች መመዘኛዎች 3.3 ቪ ናቸው።

የቦርድ ምደባ ለቦርድ ማያያዣዎች CON2

| CON2 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

CON2 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

| ፒን 1 | B13_L16_P | ወ15 | 3.3 ቪ | ፒን 2 | B14_L16_P | ቪ17 | 3.3 ቪ |

| ፒን 3 | B13_L16_N | ወ16 | 3.3 ቪ | ፒን 4 | B14_L16_N | ወ17 | 3.3 ቪ |

| ፒን 5 | B13_L15_P | T14 | 3.3 ቪ | ፒን 6 | B13_L14_P | U15 | 3.3 ቪ |

| ፒን 7 | B13_L15_N | T15 | 3.3 ቪ | ፒን 8 | B13_L14_N | ቪ15 | 3.3 ቪ |

| ፒን 9 | ጂኤንዲ | – | መሬት | ፒን 10 | ጂኤንዲ | – | መሬት |

| ፒን 11 | B13_L13_P | ቪ13 | 3.3 ቪ | ፒን 12 | B14_L10_P | AB21 | 3.3 ቪ |

| ፒን 13 | B13_L13_N | ቪ14 | 3.3 ቪ | ፒን 14 | B14_L10_N | AB22 | 3.3 ቪ |

| ፒን 15 | B13_L12_P | ወ11 | 3.3 ቪ | ፒን 16 | B14_L8_N | አአ21 | 3.3 ቪ |

| ፒን 17 | B13_L12_N | ወ12 | 3.3 ቪ | ፒን 18 | B14_L8_P | አአ20 | 3.3 ቪ |

| ፒን 19 | ጂኤንዲ | – | መሬት | ፒን 20 | ጂኤንዲ | – | መሬት |

| ፒን 21 | B13_L11_P | Y11 | 3.3 ቪ | ፒን 22 | B14_L15_N | AB20 | 3.3 ቪ |

| ፒን 23 | B13_L11_N | Y12 | 3.3 ቪ | ፒን 24 | B14_L15_P | አአ19 | 3.3 ቪ |

| ፒን 25 | B13_L10_P | ቪ10 | 3.3 ቪ | ፒን 26 | B14_L17_P | አአ18 | 3.3 ቪ |

| ፒን 27 | B13_L10_N | ወ10 | 3.3 ቪ | ፒን 28 | B14_L17_N | AB18 | 3.3 ቪ |

| ፒን 29 | ጂኤንዲ | – | መሬት | ፒን 30 | ጂኤንዲ | – | መሬት |

| ፒን 31 | B13_L9_N | አአ11 | 3.3 ቪ | ፒን 32 | B14_L6_N | T20 | 3.3 ቪ |

| ፒን 33 | B13_L9_P | አአ10 | 3.3 ቪ | ፒን 34 | B13_IO0 | Y17 | 3.3 ቪ |

| ፒን 35 | B13_L8_N | AB10 | 3.3 ቪ | ፒን 36 | B14_L7_N | ወ22 | 3.3 ቪ |

| ፒን 37 | B13_L8_P | አአ9 | 3.3 ቪ | ፒን 38 | B14_L7_P | ወ21 | 3.3 ቪ |

| ፒን 39 | ጂኤንዲ | – | መሬት | ፒን 40 | ጂኤንዲ | – | መሬት |

| ፒን 41 | B14_L11_N | ቪ20 | 3.3 ቪ | ፒን 42 | B14_L4_P | T21 | 3.3 ቪ |

| ፒን 43 | B14_L11_P | U20 | 3.3 ቪ | ፒን 44 | B14_L4_N | U21 | 3.3 ቪ |

| ፒን 45 | B14_L14_N | ቪ19 | 3.3 ቪ | ፒን 46 | B14_L9_P | Y21 | 3.3 ቪ |

| ፒን 47 | B14_L14_P | ቪ18 | 3.3 ቪ | ፒን 48 | B14_L9_N | Y22 | 3.3 ቪ |

| ፒን 49 | ጂኤንዲ | – | መሬት | ፒን 50 | ጂኤንዲ | – | መሬት |

| ፒን 51 | B14_L5_N | R19 | 3.3 ቪ | ፒን 52 | B14_L12_N | ወ20 | 3.3 ቪ |

| ፒን 53 | B14_L5_P | P19 | 3.3 ቪ | ፒን 54 | B14_L12_P | ወ19 | 3.3 ቪ |

| ፒን 55 | B14_L18_N | U18 | 3.3 ቪ | ፒን 56 | B14_L13_N | Y19 | 3.3 ቪ |

| ፒን 57 | B14_L18_P | U17 | 3.3 ቪ | ፒን 58 | B14_L13_P | Y18 | 3.3 ቪ |

| ፒን 59 | ጂኤንዲ | – | መሬት | ፒን 60 | ጂኤንዲ | – | መሬት |

| ፒን 61 | B13_L17_P | T16 | 3.3 ቪ | ፒን 62 | B14_L3_N | ቪ22 | 3.3 ቪ |

| ፒን 63 | B13_L17_N | U16 | 3.3 ቪ | ፒን 64 | B14_L3_P | U22 | 3.3 ቪ |

| ፒን 65 | B14_L21_N | P17 | 3.3 ቪ | ፒን 66 | B14_L20_N | T18 | 3.3 ቪ |

| ፒን 67 | B14_L21_P | N17 | 3.3 ቪ | ፒን 68 | B14_L20_P | R18 | 3.3 ቪ |

| ፒን 69 | ጂኤንዲ | – | መሬት | ፒን 70 | ጂኤንዲ | – | መሬት |

| ፒን 71 | B14_L22_P | P15 | 3.3 ቪ | ፒን 72 | B14_L19_N | R14 | 3.3 ቪ |

| ፒን 73 | B14_L22_N | R16 | 3.3 ቪ | ፒን 74 | B14_L19_P | P14 | 3.3 ቪ |

| ፒን 75 | B14_L24_N | R17 | 3.3 ቪ | ፒን 76 | B14_L23_P | N13 | 3.3 ቪ |

| ፒን 77 | B14_L24_P | P16 | 3.3 ቪ | ፒን 78 | B14_L23_N | N14 | 3.3 ቪ |

| ፒን 79 | B14_IO0 | P20 | 3.3 ቪ | ፒን 80 | B14_IO25 | N15 | 3.3 ቪ |

ምስል 9-2፡ ከቦርድ ወደ ቦርድ ማገናኛዎች CON2 በኮር ቦርድ ላይ

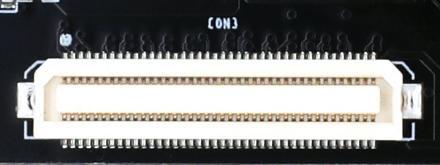

ቦርድ ወደ ቦርድ አያያዦች CON3

ባለ 80-pin አያያዥ CON3 የ FPGA BANK15 እና BANK16 መደበኛ አይኦ ለማራዘም ይጠቅማል። በተጨማሪም አራት ጄTAG ሲግናሎች ከድምጸ ተያያዥ ሞደም ቦርድ ጋር በCON3 አያያዥ በኩል ተያይዘዋል። ጥራዝtagየ BANK15 እና BANK16 ደረጃዎች በኤልዲኦ ቺፕ ሊስተካከሉ ይችላሉ። የተጫነው ነባሪው LDO 3.3 ቪ ነው። ሌሎች መደበኛ ደረጃዎችን ለማውጣት ከፈለጉ, ተስማሚ በሆነ LDO መተካት ይችላሉ.

የቦርድ ምደባ ለቦርድ ማያያዣዎች CON3

| CON3 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

CON3 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

| ፒን 1 | B15_IO0 | ጄ16 | 3.3 ቪ | ፒን 2 | B15_IO25 | M17 | 3.3 ቪ |

| ፒን 3 | B16_IO0 | F15 | 3.3 ቪ | ፒን 4 | B16_IO25 | F21 | 3.3 ቪ |

| ፒን 5 | B15_L4_P | ጂ17 | 3.3 ቪ | ፒን 6 | B16_L21_N | አ21 | 3.3 ቪ |

| ፒን 7 | B15_L4_N | ጂ18 | 3.3 ቪ | ፒን 8 | B16_L21_P | ብ21 | 3.3 ቪ |

| ፒን 9 | ጂኤንዲ | – | መሬት | ፒን 10 | ጂኤንዲ | – | መሬት |

| ፒን 11 | B15_L2_P | ጂ15 | 3.3 ቪ | ፒን 12 | B16_L23_P | E21 | 3.3 ቪ |

| ፒን 13 | B15_L2_N | ጂ16 | 3.3 ቪ | ፒን 14 | B16_L23_N | ዲ21 | 3.3 ቪ |

| ፒን 15 | B15_L12_P | ጄ19 | 3.3 ቪ | ፒን 16 | B16_L22_P | E22 | 3.3 ቪ |

| ፒን 17 | B15_L12_N | H19 | 3.3 ቪ | ፒን 18 | B16_L22_N | ዲ22 | 3.3 ቪ |

| ፒን 19 | ጂኤንዲ | – | መሬት | ፒን 20 | ጂኤንዲ | – | መሬት |

| ፒን 21 | B15_L11_P | ጄ20 | 3.3 ቪ | ፒን 22 | B16_L24_P | ጂ21 | 3.3 ቪ |

| ፒን 23 | B15_L11_N | ጄ21 | 3.3 ቪ | ፒን 24 | B16_L24_N | ጂ22 | 3.3 ቪ |

| ፒን 25 | B15_L1_N | ጂ13 | 3.3 ቪ | ፒን 26 | B15_L8_N | ጂ20 | 3.3 ቪ |

| ፒን 27 | B15_L1_P | H13 | 3.3 ቪ | ፒን 28 | B15_L8_P | H20 | 3.3 ቪ |

| ፒን 29 | ጂኤንዲ | – | መሬት | ፒን 30 | ጂኤንዲ | – | መሬት |

| ፒን 31 | B15_L5_P | ጄ15 | 3.3 ቪ | ፒን 32 | B15_L7_N | H22 | 3.3 ቪ |

| ፒን 33 | B15_L5_N | H15 | 3.3 ቪ | ፒን 34 | B15_L7_P | ጄ22 | 3.3 ቪ |

| ፒን 35 | B15_L3_N | H14 | 3.3 ቪ | ፒን 36 | B15_L9_P | K21 | 3.3 ቪ |

| ፒን 37 | B15_L3_P | ጄ14 | 3.3 ቪ | ፒን 38 | B15_L9_N | K22 | 3.3 ቪ |

| ፒን 39 | ጂኤንዲ | – | መሬት | ፒን 40 | ጂኤንዲ | – | መሬት |

| ፒን 41 | B15_L19_P | K13 | 3.3 ቪ | ፒን 42 | B15_L15_N | M22 | 3.3 ቪ |

| ፒን 43 | B15_L19_N | K14 | 3.3 ቪ | ፒን 44 | B15_L15_P | N22 | 3.3 ቪ |

| ፒን 45 | B15_L20_P | M13 | 3.3 ቪ | ፒን 46 | B15_L6_N | H18 | 3.3 ቪ |

| ፒን 47 | B15_L20_N | L13 | 3.3 ቪ | ፒን 48 | B15_L6_P | H17 | 3.3 ቪ |

| ፒን 49 | ጂኤንዲ | – | መሬት | ፒን 50 | ጂኤንዲ | – | መሬት |

| ፒን 51 | B15_L14_P | L19 | 3.3 ቪ | ፒን 52 | B15_L13_N | K19 | 3.3 ቪ |

| ፒን 53 | B15_L14_N | L20 | 3.3 ቪ | ፒን 54 | B15_L13_P | K18 | 3.3 ቪ |

| ፒን 55 | B15_L21_P | K17 | 3.3 ቪ | ፒን 56 | B15_L10_P | M21 | 3.3 ቪ |

| ፒን 57 | B15_L21_N | ጄ17 | 3.3 ቪ | ፒን 58 | B15_L10_N | L21 | 3.3 ቪ |

| ፒን 59 | ጂኤንዲ | – | መሬት | ፒን 60 | ጂኤንዲ | – | መሬት |

| ፒን 61 | B15_L23_P | L16 | 3.3 ቪ | ፒን 62 | B15_L18_P | N20 | 3.3 ቪ |

| ፒን 63 | B15_L23_N | K16 | 3.3 ቪ | ፒን 64 | B15_L18_N | M20 | 3.3 ቪ |

| ፒን 65 | B15_L22_P | L14 | 3.3 ቪ | ፒን 66 | B15_L17_N | N19 | 3.3 ቪ |

| ፒን 67 | B15_L22_N | L15 | 3.3 ቪ | ፒን 68 | B15_L17_P | N18 | 3.3 ቪ |

| ፒን 69 | ጂኤንዲ | – | መሬት | ፒን 70 | ጂኤንዲ | – | መሬት |

| ፒን 71 | B15_L24_P | M15 | 3.3 ቪ | ፒን 72 | B15_L16_P | M18 | 3.3 ቪ |

| ፒን 73 | B15_L24_N | M16 | 3.3 ቪ | ፒን 74 | B15_L16_N | L18 | 3.3 ቪ |

| ፒን 75 | NC | – | ፒን 76 | NC | – | ||

| ፒን 77 | FPGA_TCK | ቪ12 | 3.3 ቪ | ፒን 78 | FPGA_TDI | R13 | 3.3 ቪ |

| ፒን 79 | FPGA_TDO | U13 | 3.3 ቪ | ፒን 80 | FPGA_TM | T13 | 3.3 ቪ |

ምስል 9-3፡ ከቦርድ ወደ ቦርድ ማገናኛዎች CON3 በኮር ቦርድ ላይ

ቦርድ ወደ ቦርድ አያያዦች CON4

ባለ 80-ፒን አያያዥ CON4 የFPGA BANK16 መደበኛ IO እና GTP ባለከፍተኛ ፍጥነት መረጃ እና የሰዓት ምልክቶችን ለማራዘም ይጠቅማል። ጥራዝtagየ ‹IO› ወደብ የ BANK16 መደበኛ በ LDO ቺፕ ሊስተካከል ይችላል። የተጫነው ነባሪው LDO 3.3 ቪ ነው። ተጠቃሚው ሌሎች መደበኛ ደረጃዎችን ማውጣት ከፈለገ, ተስማሚ በሆነ LDO ሊተካ ይችላል. የጂቲፒ ከፍተኛ ፍጥነት ያለው መረጃ እና የሰዓት ምልክቶች በኮር ቦርዱ ላይ ጥብቅ ልዩነት አላቸው። የመረጃ መስመሮቹ በርዝመታቸው እኩል ናቸው እና የምልክት ጣልቃገብነትን ለመከላከል በተወሰነ የጊዜ ክፍተት ውስጥ ይቀመጣሉ።

የቦርድ ምደባ ለቦርድ ማያያዣዎች CON4

| CON4 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

CON4 እ.ኤ.አ. ፒን |

የተጣራ ስም |

FPGA ፒን |

ጥራዝtage ደረጃ |

| ፒን 1 | NC | – | – | ፒን 2 | – | – | |

| ፒን 3 | NC | – | – | ፒን 4 | – | – | |

| ፒን 5 | NC | – | – | ፒን 6 | – | – | |

| ፒን 7 | NC | – | – | ፒን 8 | – | – | |

| ፒን 9 | ጂኤንዲ | – | መሬት | ፒን 10 | ጂኤንዲ | – | መሬት |

| ፒን 11 | NC | – | – | ፒን 12 | MGT_TX2_P | B6 | ልዩነት |

| ፒን 13 | NC | – | – | ፒን 14 | MGT_TX2_N | A6 | ልዩነት |

| ፒን 15 | ጂኤንዲ | – | መሬት | ፒን 16 | ጂኤንዲ | – | መሬት |

| ፒን 17 | MGT_TX3_P | D7 | ልዩነት | ፒን 18 | MGT_RX2_P | ብ10 | ልዩነት |

| ፒን 19 | MGT_TX3_N | C7 | ልዩነት | ፒን 20 | MGT_RX2_N | አ10 | ልዩነት |

| ፒን 21 | ጂኤንዲ | – | መሬት | ፒን 22 | ጂኤንዲ | – | መሬት |

| ፒን 23 | MGT_RX3_P | D9 | ልዩነት | ፒን 24 | MGT_TX0_P | B4 | ልዩነት |

| ፒን 25 | MGT_RX3_N | C9 | ልዩነት | ፒን 26 | MGT_TX0_N | A4 | ልዩነት |

| ፒን 27 | ጂኤንዲ | – | መሬት | ፒን 28 | ጂኤንዲ | – | መሬት |

| ፒን 29 | MGT_TX1_P | D5 | ልዩነት | ፒን 30 | MGT_RX0_P | B8 | ልዩነት |

| ፒን 31 | MGT_TX1_N | C5 | ልዩነት | ፒን 32 | MGT_RX0_N | A8 | ልዩነት |

| ፒን 33 | ጂኤንዲ | – | መሬት | ፒን 34 | ጂኤንዲ | – | መሬት |

| ፒን 35 | MGT_RX1_P | ዲ11 | ልዩነት | ፒን 36 | MGT_CLK1_P | F10 | ልዩነት |

| ፒን 37 | MGT_RX1_N | C11 | ልዩነት | ፒን 38 | MGT_CLK1_N | E10 | ልዩነት |

| ፒን 39 | ጂኤንዲ | – | መሬት | ፒን 40 | ጂኤንዲ | – | መሬት |

| ፒን 41 | B16_L5_P | E16 | 3.3 ቪ | ፒን 42 | B16_L2_P | F16 | 3.3 ቪ |

| ፒን 43 | B16_L5_N | ዲ16 | 3.3 ቪ | ፒን 44 | B16_L2_N | E17 | 3.3 ቪ |

| ፒን 45 | B16_L7_P | ብ15 | 3.3 ቪ | ፒን 46 | B16_L3_P | C14 | 3.3 ቪ |

| ፒን 47 | B16_L7_N | ብ16 | 3.3 ቪ | ፒን 48 | B16_L3_N | C15 | 3.3 ቪ |

| ፒን 49 | ጂኤንዲ | – | መሬት | ፒን 50 | ጂኤንዲ | – | መሬት |

| ፒን 51 | B16_L9_P | አ15 | 3.3 ቪ | ፒን 52 | B16_L10_P | አ13 | 3.3 ቪ |

| ፒን 53 | B16_L9_N | አ16 | 3.3 ቪ | ፒን 54 | B16_L10_N | አ14 | 3.3 ቪ |

| ፒን 55 | B16_L11_P | ብ17 | 3.3 ቪ | ፒን 56 | B16_L12_P | ዲ17 | 3.3 ቪ |

| ፒን 57 | B16_L11_N | ብ18 | 3.3 ቪ | ፒን 58 | B16_L12_N | C17 | 3.3 ቪ |

| ፒን 59 | ጂኤንዲ | – | መሬት | ፒን 60 | ጂኤንዲ | – | መሬት |

| ፒን 61 | B16_L13_P | C18 | 3.3 ቪ | ፒን 62 | B16_L14_P | E19 | 3.3 ቪ |

| ፒን 63 | B16_L13_N | C19 | 3.3 ቪ | ፒን 64 | B16_L14_N | ዲ19 | 3.3 ቪ |

| ፒን 65 | B16_L15_P | F18 | 3.3 ቪ | ፒን 66 | B16_L16_P | ብ20 | 3.3 ቪ |

| ፒን 67 | B16_L15_N | E18 | 3.3 ቪ | ፒን 68 | B16_L16_N | አ20 | 3.3 ቪ |

| ፒን 69 | ጂኤንዲ | – | መሬት | ፒን 70 | ጂኤንዲ | – | መሬት |

| ፒን 71 | B16_L17_P | አ18 | 3.3 ቪ | ፒን 72 | B16_L18_P | F19 | 3.3 ቪ |

| ፒን 73 | B16_L17_N | አ19 | 3.3 ቪ | ፒን 74 | B16_L18_N | F20 | 3.3 ቪ |

| ፒን 75 | B16_L19_P | ዲ20 | 3.3 ቪ | ፒን 76 | B16_L20_P | C22 | 3.3 ቪ |

| ፒን 77 | B16_L19_N | C20 | 3.3 ቪ | ፒን 78 | B16_L20_N | ብ22 | 3.3 ቪ |

| ፒን 79 | NC | – | ፒን 80 | NC | – |

ምስል 9-4፡ ከቦርድ ወደ ቦርድ ማገናኛዎች CON4 በኮር ቦርድ ላይ

ክፍል 10: የኃይል አቅርቦት

የAC7A200 FPGA ኮር ቦርዱ በDC5V በድምጸ ተያያዥ ሞደም የሚሰራ ሲሆን ለብቻው ጥቅም ላይ ሲውል በሚኒ ዩኤስቢ በይነገጽ ነው የሚሰራው። እባካችሁ ጉዳት እንዳይደርስባችሁ በአንድ ጊዜ በሚኒ ዩኤስቢ እና በአገልግሎት አቅራቢው ቦርዱ ሃይል እንዳታቀርቡ ተጠንቀቁ። በቦርዱ ላይ ያለው የኃይል አቅርቦት ንድፍ ንድፍ በስእል 10-1 ይታያል.

ምስል 10-1፡ የኃይል አቅርቦት በኮር ቦርድ ንድፍ ላይ

የኮር ቦርዱ በ+5V እና ወደ +3.3V፣+1.5V፣+1.8V፣+1.0V ባለአራት መንገድ የሃይል አቅርቦት በሶስት ዲሲ/ዲሲ የሃይል አቅርቦት ቺፕ TLV62130RGT ተቀይሯል። የ +1.0V ጅረት እስከ 6A ሊደርስ ይችላል፣ እና ሌሎቹ ሶስት የውጤት ሞገዶች እስከ 3A ሊሆኑ ይችላሉ። VCCIO የተፈጠረው በአንድ LDOSPX3819M5-3-3 ነው። VCCIO በዋናነት ለ BANK15 እና BANK16 የFPGA ሃይል ያቀርባል። ተጠቃሚዎች የ BANK15,16 IOን ወደ ተለየ ጥራዝ መቀየር ይችላሉtagየ LDO ቺፕን በመተካት e ደረጃዎች. 1.5V VTT እና VREF ጥራዝ ያመነጫል።tagበ DDR3 በTI TPS51200 የሚፈለግ። የ MGTAVTT እና MGTAVCC የ1.8V ሃይል አቅርቦት ለጂቲፒ ትራንስሴይቨር የሚመነጨው በTI TPS74801 ቺፕ ነው። የእያንዳንዱ የኃይል ማከፋፈያ ተግባራት በሚከተለው ሠንጠረዥ ውስጥ ይታያሉ.

| የኃይል አቅርቦት | ተግባር |

| + 1.0 ቪ | FPGA ኮር ጥራዝtage |

| + 1.8 ቪ | FPGA ረዳት ጥራዝtagሠ, TPS74801 የኃይል አቅርቦት |

| + 3.3 ቪ | VCCIO of Bank0፣Bank13 እና Bank14 of FPGA፣QSIP FLASH፣Clock Crystal |

| + 1.5 ቪ | DDR3፣ Bank34 እና Bank35 የFPGA |

| VREF፣VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA ባንክ15, ባንክ16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 የ FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 የ FPGA |

የ Artix-7 FPGA የኃይል አቅርቦት የኃይል-ተከታታይ መስፈርት ስላለው በወረዳው ንድፍ ውስጥ, በቺፑ የኃይል መስፈርቶች መሰረት አዘጋጅተናል, እና የኃይል ማመንጫው 1.0V-> 1.8V-> (1.5) ነው. V, 3.3V, VCCIO) እና 1.0V-> MGTAVCC -> MGTAVTT, የቺፑን መደበኛ አሠራር ለማረጋገጥ የወረዳ ንድፍ.

በ AC7A200 FPGA ኮር ቦርድ ላይ ያለው የኃይል ዑደት በስእል 10-2 ይታያል፡

ምስል 10-2፡ በAC7A200 FPGA ኮር ቦርድ ላይ የኃይል አቅርቦት

ክፍል 11: የመጠን ልኬት

ምስል 11-1፡ AC7A200 FPGA ኮር ቦርድ (ከፍተኛ View)

ምስል 11-2፡ AC7A200 FPGA ኮር ሰሌዳ (ታች View)

ሰነዶች / መርጃዎች

|

ALINX AC7A200 ARTIX-7 FPGA ልማት ቦርድ [pdf] የተጠቃሚ መመሪያ AC7A200 ARTIX-7 FPGA ልማት ቦርድ፣ AC7A200፣ ARTIX-7 FPGA ልማት ቦርድ፣ FPGA ልማት ቦርድ፣ ልማት ቦርድ፣ ቦርድ |