ኢንቴል ከፍተኛ-ደረጃ ሲንቴሲስ ማጠናከሪያ ፕሮ እትም።

የምርት መረጃ

| የምርት ስም | Intel High-Level Synthesis Compiler Pro እትም |

|---|---|

| ሥሪት | 22.4 |

| የተለቀቀበት ቀን | ዲሴምበር 19፣ 2022 |

| የማቋረጥ ማስታወቂያ | የIntel High-Level Synthesis Compiler እንዲሆን ታቅዷል ከስሪት 23.4 በኋላ ተቋርጧል። |

የምርት አጠቃቀም መመሪያዎች

የመነሻ መመሪያ

- የአቀናባሪ አካባቢዎን ያስጀምሩ።

- Review የተለያዩ ንድፍ ለምሳሌampከ Intel HLS Compiler ጋር የቀረቡ ትምህርቶች እና ትምህርቶች።

የተጠቃሚ መመሪያ

- የተጠቃሚ መመሪያው በ ላይ መመሪያዎችን ይሰጣል

- ለኢንቴል FPGA ምርቶች የተነደፈ የአእምሮአዊ ንብረት (IP)ን ማዋሃድ፣ ማረጋገጥ እና ማስመሰል።

- የእርስዎን አካል ከመፍጠር እና የሙከራ ቤንች እስከ ኢንቴል ኳርትስ ፕራይም ሶፍትዌሮች ጋር ወደ ትልቅ ስርዓት እስከማዋሃድ ድረስ የክፍልዎን አጠቃላይ የእድገት ፍሰት ማለፍ።

ምርጥ ልምዶች መመሪያ

የምርጥ የተግባር መመሪያ የ FPGA አካባቢ አጠቃቀምን እና የ HLS ክፍልዎን አፈጻጸም ለማሻሻል ሊያመለክቱ የሚችሉ ቴክኒኮችን እና ልምዶችን ይሰጣል። የክፍልዎን ተግባራዊ ትክክለኛነት ካረጋገጡ በኋላ እነዚህን ምርጥ ልምዶች ይተግብሩ።

የማጣቀሻ መመሪያ

የማጣቀሻ መመሪያው በIntel HLS Compiler ስለሚደገፉ ባህሪያት የማመሳከሪያ መረጃን ይሰጣል። በ Intel HLS Compiler ትዕዛዝ አማራጮች ላይ ዝርዝሮችን ያግኙ, ራስጌ files፣ pragmas፣ ባሕሪዎች፣ ማክሮዎች፣ መግለጫዎች፣ ክርክሮች እና አብነት ቤተ-መጻሕፍት።

Intel® High Level Synthesis Compiler Pro እትም ስሪት 22.4 የመልቀቂያ ማስታወሻዎች

- የIntel® High Level Synthesis Compiler Pro Edition Release Notes ስለ Intel High Level Synthesis Compiler Pro Edition ስሪት 22.4 ዘግይቶ ሰበር መረጃን ይሰጣል።

በመጠባበቅ ላይ ያለው የኢንቴል ኤች.ኤል.ኤስ

- የቅርብ ጊዜዎቹን የFPGA ባለከፍተኛ ደረጃ ዲዛይን ባህሪያት፣ ማሻሻያዎች እና የልማት መገልገያዎች መዳረሻን ለማቆየት፣ የIntel oneAPI Base Toolkitን ለመጠቀም ነባር ንድፎችዎን ያዛውሩ።

- የIntel High Level Synthesis (HLS) Compiler ከስሪት 23.4 በኋላ እንዲቋረጥ ታቅዷል።

- ለስደት ምክር የIntel oneAPI ምርት ገጽን ይጎብኙ ወይም ለማንኛውም ጥያቄዎች ወይም ጥያቄዎች ወደ Intel High Level Design Community መድረክ ይሂዱ።

ስለ Intel HLS Compiler Pro Edition Documentation Library

- የIntel HLS Compiler Pro እትም ሰነድ በጥቂት ህትመቶች ተከፋፍሏል። የሚፈልጉትን የIntel HLS Compiler Pro Edition መረጃ የያዘውን ህትመት ለማግኘት የሚከተለውን ሰንጠረዥ ይጠቀሙ፡-

ሠንጠረዥ 1. Intel High-Level Synthesis Compiler Pro Edition Documentation Library

| ርዕስ እና መግለጫ | |

| የመልቀቂያ ማስታወሻዎች

ስለ Intel HLS Compiler ዘግይቶ ሰበር መረጃን ያቀርባል። |

አገናኝ |

| የመነሻ መመሪያ

የአቀናባሪ አካባቢዎን እንዴት ማስጀመር እንደሚችሉ በመማር ከIntel HLS Compiler ጋር ተነሱ እና ይሮጡviewየተለያዩ ንድፍ ለምሳሌampከ Intel HLS Compiler ጋር የቀረቡ ትምህርቶች እና ትምህርቶች። |

አገናኝ |

| የተጠቃሚ መመሪያ

ለኢንቴል FPGA ምርቶች የነደፉትን የአእምሮአዊ ንብረት (IP)ን ስለማዋሃድ፣ ስለማረጋገጥ እና ስለማስመሰል መመሪያዎችን ይሰጣል። የእርስዎን አካል ከመፍጠር እና የፈተና ቤንች እስከ ኢንቴል ኳርትስ ፕራይም ሶፍትዌሮች ጋር ወደ ትልቅ ስርዓት እስከማዋሃድ ድረስ አጠቃላይ የአካልዎን የእድገት ፍሰት ይሂዱ። |

አገናኝ |

| ምርጥ ልምዶች መመሪያ

የእርስዎን HLS ክፍል የFPGA አካባቢ አጠቃቀምን እና አፈጻጸምን ለማሻሻል ማመልከት የሚችሏቸውን ቴክኒኮችን እና ልምዶችን ያቀርባል። በተለምዶ፣ የእርስዎን አካል ተግባራዊነት ትክክለኛነት ካረጋገጡ በኋላ እነዚህን ምርጥ ልምዶች ይተገብራሉ። |

አገናኝ |

| የማጣቀሻ መመሪያ

በIntel HLS Compiler ስለሚደገፉ ባህሪያት ማጣቀሻ መረጃ ይሰጣል። በ Intel HLS Compiler ትዕዛዝ አማራጮች ላይ ዝርዝሮችን ያግኙ, ራስጌ files፣ pragmas፣ ባሕሪዎች፣ ማክሮዎች፣ መግለጫዎች፣ ክርክሮች እና አብነት ቤተ-መጻሕፍት። |

አገናኝ |

ኢንቴል ኮርፖሬሽን. መብቱ በህግ የተጠበቀ ነው. ኢንቴል፣ የኢንቴል አርማ እና ሌሎች የኢንቴል ምልክቶች የኢንቴል ኮርፖሬሽን ወይም የስርጭቱ የንግድ ምልክቶች ናቸው። ኢንቴል የኤፍፒጂኤ እና ሴሚኮንዳክተር ምርቶቹን በIntel መደበኛ ዋስትና መሰረት ለአሁኑ ዝርዝር መግለጫዎች ዋስትና ይሰጣል፣ነገር ግን በማናቸውም ምርቶች እና አገልግሎቶች ላይ ያለማሳወቂያ በማንኛውም ጊዜ ለውጦችን የማድረግ መብቱ የተጠበቀ ነው። ኢንቴል በዚህ ውስጥ የተገለጸውን ማንኛውንም መረጃ፣ ምርት ወይም አገልግሎት ከመተግበሩ ወይም ከመጠቀሙ የተነሳ ምንም አይነት ሃላፊነት ወይም ተጠያቂነት አይወስድም። የኢንቴል ደንበኞች በማናቸውም የታተመ መረጃ ላይ ከመታመንዎ በፊት እና ለምርቶች ወይም አገልግሎቶች ትእዛዝ ከማስቀመጥዎ በፊት የቅርብ ጊዜውን የመሳሪያ ዝርዝሮችን እንዲያገኙ ይመከራሉ።

*ሌሎች ስሞች እና የንግድ ምልክቶች እንደሌሎች ንብረት ሊጠየቁ ይችላሉ።

በመጠባበቅ ላይ ያለው የኢንቴል ኤች.ኤል.ኤስ

- የቅርብ ጊዜዎቹን የFPGA ባለከፍተኛ ደረጃ ዲዛይን ባህሪያት፣ ማሻሻያዎች እና የልማት መገልገያዎች መዳረሻን ለማቆየት፣ የIntel oneAPI Base Toolkitን ለመጠቀም ነባር ንድፎችዎን ያዛውሩ።

- የIntel High Level Synthesis (HLS) Compiler ከስሪት 23.4 በኋላ እንዲቋረጥ ታቅዷል።

- ለስደት ምክር የIntel oneAPI ምርት ገጽን ይጎብኙ ወይም ለማንኛውም ጥያቄዎች ወይም ጥያቄዎች ወደ Intel High Level Design Community መድረክ ይሂዱ።

አዲስ ባህሪዎች እና ማሻሻያዎች

- የIntel High Level Synthesis Compiler Pro Edition ስሪት 22.4 የሚከተሉትን አዲስ ባህሪያት ያካትታል፡

- የጥገና መለቀቅ።

- ለIntel HLS Compiler Pro Edition ስሪት 22.4 ምንም አዲስ ባህሪያት ወይም ማሻሻያዎች የሉም።

በሶፍትዌር ባህሪ ላይ ለውጦች

- ይህ ክፍል የIntel HLS Compiler Pro Edition ስሪት 22.4 ባህሪያት ከአቀናባሪው ቀደም ብለው ከተለቀቁት የተለወጡባቸውን አጋጣሚዎች ይመዘግባል።

የጥገና መለቀቅ።

- ለIntel HLS Compiler Pro Edition ስሪት 22.4 በሶፍትዌር ባህሪ ላይ ምንም ለውጦች የሉም።

Intel High-Level Synthesis Compiler Pro Edition ቅድመ ተፈላጊዎች

- የIntel HLS Compiler Pro እትም የIntel Quartus® Prime Pro Edition Design Suite አካል ነው። የኢንቴል ኤችኤልኤስ ኮምፕሌተርን እንደ ኢንቴል ኳርተስ ፕራይም ሶፍትዌር ጭነት አካል አድርገው መጫን ወይም ለየብቻ መጫን ይችላሉ። ለመጠቀም Intel Quartus Prime እና ተጨማሪ ሶፍትዌሮችን ይፈልጋል።

- የስርዓት መስፈርቶችን፣ ቅድመ ሁኔታዎችን እና የፈቃድ መስፈርቶችን ጨምሮ ኢንቴል ኳርተስ ፕራይም ፕሮ እትም ሶፍትዌርን ስለመጫን ዝርዝር መመሪያዎችን ለማግኘት የIntel FPGA ሶፍትዌር ጭነት እና ፍቃድን ይመልከቱ።

- Intel HLS Compiler ከ Intel Quartus Prime በተጨማሪ የሚከተለውን ሶፍትዌር ይፈልጋል፡-

C ++ ማጠናከሪያ

- በሊኑክስ ላይ፣ Intel HLS Compiler የጂኤንዩ ሲ++ ላይብረሪ እና ሁለትዮሽ መገልገያዎችን (ቢኒትልስ) ጨምሮ GCC 9.3.0 ይፈልጋል።

- ይህ የጂሲሲ ስሪት እንደ ኢንቴል ኤችኤልኤስ ኮምፕሌተር ጭነት አካል ሆኖ ቀርቧል። Intel HLS Compiler ከጫኑ በኋላ GCC 9.3.0 በ ውስጥ ይገኛል። /ጂሲሲ.

- ጠቃሚ፡- የኢንቴል ኤች.ኤል.ኤስ. ኮምፕሌተር ይጠቀማል / gcc ማውጫ እንደ የመሳሪያ ሰንሰለት ማውጫ። ይህንን የጂሲሲ ጭነት ለሁሉም ከኤችኤልኤስ ጋር ለተያያዙ የንድፍ ስራዎች ይጠቀሙ።

- ለዊንዶውስ፣ ከሚከተሉት የ Microsoft* Visual Studio* ፕሮፌሽናል ስሪቶች ውስጥ አንዱን ጫን፡-

- የማይክሮሶፍት ቪዥዋል ስቱዲዮ 2017 ፕሮፌሽናል

- የማይክሮሶፍት ቪዥዋል ስቱዲዮ 2017 ማህበረሰብ

- በጣም ወቅታዊውን የC++17 ድጋፍ ለማግኘት የቅርብ ጊዜውን የ Visual Studio 2017 ስሪት እየተጠቀሙ መሆንዎን ያረጋግጡ።

- ጠቃሚ፡- የIntel HLS Compiler ሶፍትዌር ለሶፍትዌሩ እትም ከተገለጹት በስተቀር የማይክሮሶፍት ቪዥዋል ስቱዲዮን አይደግፍም።

ሲመንስ * EDA Questa® የማስመሰል ሶፍትዌር

- በዊንዶውስ እና ሬድሃት ሊኑክስ ሲስተምስ የ Questa® simulation ሶፍትዌርን ከ Intel Quartus Prime ሶፍትዌር ጫኚ መጫን ትችላለህ። ያሉት አማራጮች የሚከተሉት ናቸው።

- Questa Intel FPGA እትም

- Questa Intel FPGA ማስጀመሪያ እትም

- ሁለቱም Questa Intel FPGA እትም እና Questa Intel FPGA ማስጀመሪያ እትም ፈቃድ ያስፈልጋቸዋል። የQuesta Intel FPGA ማስጀመሪያ እትም ፍቃድ ነጻ ነው። ለዝርዝሮች፣ የIntel FPGA ሶፍትዌር ጭነት እና ፍቃድ ይመልከቱ።

- በአማራጭ፣ የራስዎን ፍቃድ ያለው የ Siemens* EDA ModelSim* SE ወይም Siemens EDA Questa Advanced Simulator ሶፍትዌርን መጠቀም ይችላሉ።

- በሊኑክስ ሲስተምስ ላይ፣ Questa – Intel FPGA Edition እና Questa – Intel FPGA Starter Edition የቀይ ኮፍያ * ማሻሻያ መሳሪያዎች ፓኬጆችን ይፈልጋሉ።

- የኢንቴል ሶፍትዌሩ ስለሚደግፋቸው የሞዴል ሲም እና የ Questa የሶፍትዌር ስሪቶች ሁሉ መረጃ ለማግኘት ለኢንቴል ኳርተስ ፕራይም ፕሮ እትም እትም በሶፍትዌር እና በመሳሪያ ድጋፍ መልቀቂያ ማስታወሻዎች ውስጥ ያለውን የኢዲኤ በይነገጽ መረጃ ክፍል ይመልከቱ።

ተዛማጅ መረጃ

- Intel High Level Synthesis Compiler አጀማመር መመሪያ

- የሚደገፉ ስርዓተ ክወናዎች

- በ Intel FPGA ሶፍትዌር ጭነት እና ፍቃድ ውስጥ የሶፍትዌር መስፈርቶች

- የኢዲኤ በይነገጽ መረጃ (Intel Quartus Prime Pro እትም)

የታወቁ ጉዳዮች እና መፍትሄዎች

- ይህ ክፍል በIntel HLS Compiler Pro Edition Version 22.4 ላይ ተጽዕኖ ስለሚያሳድሩ የታወቁ ጉዳዮች መረጃን ይሰጣል።

| መግለጫ | የማጣራት ስራ |

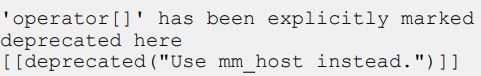

| የተቋረጠውን ክፍል mm_master ሲጠቀሙ አቀናባሪው የሚከተለውን የማስጠንቀቂያ መልእክት ያስተላልፋል፡-

ይህ መልእክት የትኛው የኮድዎ ክፍል መቀየር እንዳለበት አያመለክትም። |

የተቋረጠውን ክፍል mm_master የሚተካውን mm_host ክፍል በመጠቀም ይህንን የማስጠንቀቂያ መልእክት ያስወግዱ። |

| (ዊንዶውስ ብቻ) ረጅም የመንገድ ስም ባለው ማውጫ ውስጥ ንድፍ ማጠናቀር ወደ ማጠናቀር ውድቀቶችን ያስከትላል።

debug.log ን ይመልከቱ file " ማግኘት አልተቻለም file"ስህተቶች. እነዚህ ስህተቶች የእርስዎ መንገድ በጣም ረጅም መሆኑን ሊያመለክቱ ይችላሉ። |

አጭር የመንገድ ስም ባለው ማውጫ ውስጥ ንድፉን ያጠናቅቁ። |

| (ዊንዶውስ ብቻ) ለኢንቴል ኳርትስ ፕራይም መጫኛ ማውጫ ያለው ረጅም መንገድ የIntel HLS Compiler መማሪያዎችን እና የቀድሞን በተሳካ ሁኔታ እንዳጠናቀሩ እና እንዳያስኬዱ ይከለክላል።ample ንድፎች.

debug.log ን ይመልከቱ file " ማግኘት አልተቻለም file"ስህተቶች. እነዚህ ስህተቶች የእርስዎ መንገድ በጣም ረጅም መሆኑን ሊያመለክቱ ይችላሉ። |

አጋዥ ስልጠናዎቹን ይውሰዱ እና ለምሳሌampእነሱን ለማስኬድ ከመሞከርዎ በፊት ወደ አጭር መንገድ ስም። |

| መግለጫ | የማጣራት ስራ |

| OpenCL* ላይ ያነጣጠሩ እና በኤችኤልኤስ የተፃፉ ቤተ-መጻሕፍት ዥረቶችን ወይም ቧንቧዎችን በ OpenCL ኮድ እና በHLS ውስጥ በተፃፈው ቤተ-መጽሐፍት መካከል እንደ መገናኛ መጠቀም አይችሉም።

ነገር ግን፣ ሁለቱም የመጨረሻ ነጥቦች በቤተ መፃህፍቱ ውስጥ ካሉ (ለምሳሌ ፣ ለምሳሌ) በኤችኤልኤስ ያለው ቤተ-መጽሐፍት ዥረቶችን ወይም ቧንቧዎችን መጠቀም ይችላል።ample, ሁለት የተግባር ተግባራትን የሚያገናኝ ዥረት). |

ኤን/ኤ |

| የihc:: maxburst መለኪያውን ወደ Avalon® Memory-Mapped host በይነ መጠቀሚያዎች መተግበር ንድፍዎ በሲሙሌሽን ውስጥ እንዲንጠለጠል ሊያደርግ ይችላል። | ኤን/ኤ |

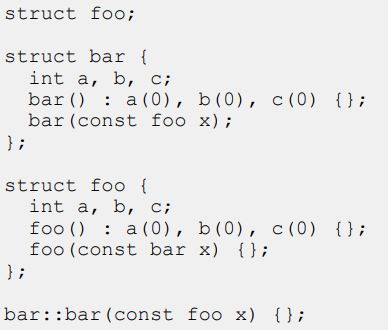

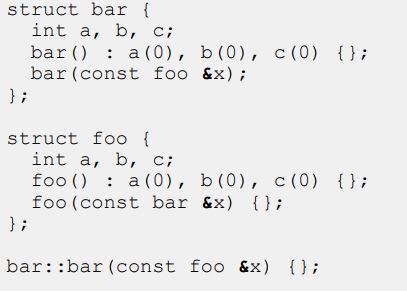

| በአንዳንድ ያልተለመዱ ሁኔታዎች፣ ሁለት ክፍሎች ካሉዎት ግንበኞች እያንዳንዳቸው የሌላውን ክፍል እንደ ግብአት የሚሹ ከሆነ፣ ማጠናከሪያው ሊበላሽ ይችላል።

ለ example፣ የሚከተለውን የኮድ ቅንጣቢ ማጠናቀር አቀናባሪው እንዲሰበር ያደርገዋል፡-

|

ክብ ፍቺ ከመፍጠር ተቆጠብ። በምትኩ፣ በእርስዎ ቅጂ ገንቢ ውስጥ ጠቋሚ ወይም ማጣቀሻ ይጠቀሙ።

ለ example፣ የቀደመውን የኮድ ቅንጣቢ ወደሚከተለው ኮድ ቀይር እና በህንፃው ውስጥ ለግንባታ ማመሳከሪያነት ያስተላልፉ።

|

| OpenCL ላይ ያነጣጠሩ እና በኤችኤልኤስ የተፃፉ ቤተ-መጻሕፍት ቤተ መፃህፍቱን የሚያካትቱ የOpenCL ከርነሎች የበለጠ ወግ አጥባቂ ጭማሪ ስብስብ እንዲኖራቸው ሊያደርጉ ይችላሉ። | ኤን/ኤ |

| ቤተ-መጽሐፍት በሚገነቡበት ጊዜ፣ በኋላ ላይ በ#ፕራግማ ውስጥ የሚጠቀሙበትን እሴት የሚገልጽ #define ካለዎት የfpga_crossgen ትዕዛዝ አይሳካም።

ለ example, የሚከተለው ኮድ በ

|

ከ #ፕራግማ ይልቅ ፕራግማ ይጠቀሙ።

ለ example፣ የሚከተለው በተሳካ ሁኔታ ያጠናቅራል።

|

| የተለየ ማጠናቀር እና ማገናኘት s እንዲኖርዎት የ -c ትዕዛዝ አማራጭን ሲጠቀሙtages በእርስዎ የስራ ሂደት ውስጥ፣ እና የ-march አማራጭን በ linking s ውስጥ ካልገለጹtagሠ (ወይም የተለየ -ማርች አማራጭ እሴት ይግለጹ)፣ የእርስዎ አገናኝ stagከስህተት መልዕክቶች ጋር ወይም ያለሱ ሊሳካ ይችላል። | ለሁለቱም ከ -c ትእዛዝ አማራጭ s ጋር አንድ አይነት የማርች አማራጭ ዋጋ መጠቀምዎን ያረጋግጡtagሠ እና ማገናኛ stage. |

| መግለጫ | የማጣራት ስራ |

| የhls_merge ማህደረ ትውስታ ባህሪ ባልተጠቀለለ ወይም ከፊል ባልተጠቀለለ loop ውስጥ በተገለፀው ድርድር ላይ መተግበር የድርድር ቅጂዎች ባልተጠቀለሉ የloop ድግግሞሾች ላይ እንዲዋሃዱ ያደርጋል።

|

የhls_merge ማህደረ ትውስታ ባህሪን ባልተጠቀለሉ loops ውስጥ ከመጠቀም ይቆጠቡ።

ባልተጠቀለለ ሉፕ ውስጥ ትውስታዎችን ማዋሃድ ካስፈለገዎት ወርድ ለመዋሃድ የድርድር አይነትን በግልፅ ያሳውቁ ወይም ለጥልቅ ውህደት ጥልቅ ድርድር ያሳውቁ።

|

| በተግባር ማህደረ ትውስታ ውስጥ Viewየከፍተኛ ደረጃ ዲዛይን ሪፖርት፣ አንዳንድ ተግባር-ተኮር ትውስታዎች እንደ “የተመቻቹ” ሊመስሉ ይችላሉ። | ምንም።

መቼ ሀ file አካላት ያልሆኑ ተግባራትን እና አካላትን ያካትታል ፣ ሁሉም የተግባር-ተኮር ተለዋዋጮች በተግባራዊ ማህደረ ትውስታ ዝርዝር ውስጥ ተዘርዝረዋል ፣ ግን ከክፍሎች የመጡ ተለዋዋጮች ብቻ ስለእነሱ መረጃ በተግባራዊ ማህደረ ትውስታ ውስጥ ይታያሉ። View መቃን |

| አንዳንድ የከፍተኛ ደረጃ ዲዛይን ሪፖርቶች በማይክሮሶፍት ኢንተርኔት ኤክስፕሎረር* ውስጥ አልተሳኩም። | ከሚከተሉት አሳሾች አንዱን ይጠቀሙ view ዘገባዎቹ፡-

• ጉግል ክሮም* • ማይክሮሶፍት ጠርዝ* • ሞዚላ ፋየር ፎክስ* |

| ሉፕ Viewበከፍተኛ ደረጃ ዲዛይን ሪፖርቶች ውስጥ የሚከተሉት ገደቦች አሏቸው

• ከድንኳን ነጻ የሆኑ ስብስቦች ባህሪ በ Loop ውስጥ አልተቀረጸም። Viewኧረ በ Loop ውስጥ የሚታየው የመጨረሻው መዘግየት Viewከስቶል-ነጻ ክላስተር ከትክክለኛው የንድፍዎ መዘግየት የበለጠ ተስፋ አስቆራጭ (ማለትም ከፍ ያለ) ነው። ከስብስብ እና ከድንኳን-ነጻ ዘለላዎች መግለጫ ለማግኘት፣ ይመልከቱ የውሂብ ዱካውን በማሰባሰብ ላይ በውስጡ ኢንቴል ከፍተኛ-ደረጃ Synthesis Compiler Pro እትም ምርጥ የተግባር መመሪያ. • ከማህደረ ትውስታ ወይም ከህትመት መግለጫዎች የተነበቡ እና የሚጽፉ ድንኳኖች ሞዴል አይደሉም። • ከፍተኛ ድግግሞሽ ቆጠራዎች (> 1000) የሉፕ ዝግተኛ አፈጻጸም ያስከትላሉ Viewኧረ • በ Loop ውስጥ የዜሮ (0) ድግግሞሽ ብዛት መግለጽ አይችሉም Viewኧረ |

ምንም። |

| በዊንዶውስ ሲስተሞች ላይ በተፈጠሩት የከፍተኛ ደረጃ ዲዛይን ሪፖርቶች ውስጥ በአንዳንድ ሪፖርቶች ውስጥ ያሉ አገናኞች አይሰሩም። | በሊኑክስ ሲስተም የከፍተኛ ደረጃ ዲዛይን ሪፖርቶችን (ማለትም የእርስዎን ኮድ ያጠናቅቁ)። |

| ፓኬቶችን በሚጠቀም የእንፋሎት በይነገጽ ውስጥ የአንድ አክ_ኢንት ዳታ አይነት struct መጠቀም (ihc ::usesPackets) ) አይሰራም።

ለ example፣ የሚከተለው የኮድ ቅንጣቢ አይሰራም።

|

ይህንን ጥምረት በንድፍዎ ውስጥ ለመጠቀም የሚከተሉትን ገደቦች ያክብሩ።

• የውስጣዊ አካውንት ዳታ መጠን የ8 ብዜት መሆን አለበት። • የዥረት በይነገጽ አይነት መግለጫ መገለጽ አለበት። ihc:: bitsPerSymbol<8> ለ example፣ የሚከተለው የኮድ ቅንጣቢ ይሰራል፡

|

| መግለጫ | የማጣራት ስራ | |

| የኢንqueue ተግባር ጥሪዎችን በመጠቀም ከፍተኛ-throughput የእርስዎን አካል ሲሙሌሽን ሲያካሂዱ የihc_hls_component_run_all ተግባርን ካልተጠቀምክ ሁሉም የ ihc_hls_enqueue ጥሪዎች ከተጠሩ በኋላ የሚከተሉት ባህሪያት ይከሰታሉ፡

• በምሳሌነት፣ የታሰሩ አካላት ተግባራት ይከናወናሉ። • በሲሙሌሽን ውስጥ፣ የታሰሩ አካላት ተግባራት አይሰሩም፣ ምንም ስህተት ወይም የማስጠንቀቂያ መልእክቶች አልተሰጡም። |

ከ ihc_hls_enqueue ጥሪዎች በኋላ የihc_hls_component_run_all ተግባር መጠቀማችሁን አረጋግጥ። | |

| የተግባር ተግባርን በihc ::ማስጀመር_ሁልጊዜ_አሂድ ማስጀመር | ማመቻቸትን ለማስወገድ ትንሽ ጊዜ ይጨምሩ (1) | |

| በስራው ላይ የተተገበሩትን የማመቻቸት ባህሪያትን ያስወግዳል | ለተጎዳው ተግባር loop ተጓዳኝ መቆጣጠሪያውን ይተግብሩ | |

| ተግባር. | ከተግባሩ ይልቅ ፕራግማ ወደ ጊዜ (1) loop። | |

| በሚከተለው ኮድ example, በተግባሩ ላይ የተተገበረው ባህሪ ችላ ይባላል. የከፍተኛ ደረጃ ዲዛይን ሪፖርቶች ከተጠየቀው II ከ 1 ይልቅ ለዚህ ተግባር II የ 4 ያሳያሉ። | የሚከተለው ኮድ እ.ኤ.አ.ampይህንን ለውጥ ለቀድሞው ኮድ እንዴት ተግባራዊ ማድረግ እንደምትችል አሳይampላይ: | |

|

|

|

| በርካታ የኤችኤልኤስ ክፍሎችን ለያዙ የሳይክሎን® V ፕሮጀክቶች፣ ፕሮጀክትህን ወደ ሃርድዌር (i++ -march=CycloneV) ለማጠናቀር የi++ ትዕዛዝን ስትጠቀም ስህተት ሊደርስብህ ይችላል።

በፕሮጀክትዎ ላይ በመመስረት የስህተት ፅሁፉ ቢለያይም የስህተት ፊርማው በመጥፎ የVerilog አገባብ ምክንያት የIntel Quartus Prime ማጠናቀር አለመሳካት ነው። አንድ ሞጁል የኢንቴል ኳርትስ ፕራይም አቀናባሪ ሊያገኘው ያልቻለውን ተግባር ለመጠቀም ይሞክራል። |

ይህ ችግር ካጋጠመዎት እያንዳንዱን የ HLS አካል በተለየ ፕሮጀክት ውስጥ ያስቀምጡ። | |

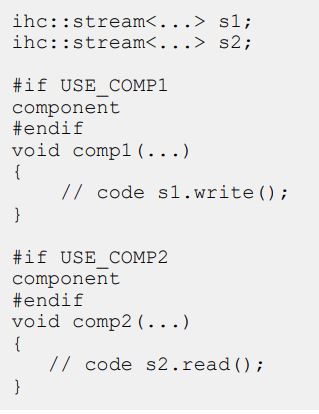

| ብዙ አካላትን የያዙ አንዳንድ ንድፎችን ማጠናቀር በዥረት መልሶ መጠቀም ላይ ስህተት ይፈጥራል። | ይህ ጉዳይ ካጋጠመዎት, በንድፍ ውስጥ ያለውን እያንዳንዱን አካል በተናጠል ያጠናቅቁ. እያንዳንዱ አካል ለብቻው እንዲጠናቀር ለማስቻል ወደ ኮድዎ ማክሮዎችን ማከል ሊኖርብዎ ይችላል። | |

| እስቲ የሚከተለውን ተመልከትampላይ: | ||

|

||

Intel High-Level Synthesis Compiler Pro እትም የልቀት ማስታወሻዎች ማህደሮች

ለዚህ የተጠቃሚ መመሪያ ለቅርብ ጊዜ እና ቀዳሚ ስሪቶች፣ Intel HLS Compiler Pro Edition Release Notes የሚለውን ይመልከቱ። የሶፍትዌር ሥሪት ካልተዘረዘረ ለቀድሞው የሶፍትዌር ሥሪት የመልቀቂያ ማስታወሻዎች ተፈጻሚ ይሆናሉ።

የሰነድ ማሻሻያ ታሪክ ለኢንቴል ኤችኤልኤስ ማጠናከሪያ ፕሮ እትም ሥሪት 22.4 የመልቀቂያ ማስታወሻዎች

| የሰነድ ሥሪት | ኢንቴል ኳርትስ ዋና ስሪት | ለውጦች |

| 2022.12.19 | 22.4 | • የመጀመሪያ መለቀቅ። |

ሰነዶች / መርጃዎች

|

ኢንቴል ከፍተኛ ደረጃ ሲንቴሲስ ማጠናከሪያ ፕሮ እትም። [pdf] መመሪያ ሥሪት 22.4፣ ሥሪት 23.4፣ የከፍተኛ ደረጃ ውህድ አቀናባሪ ፕሮ እትም፣ ከፍተኛ ደረጃ ውህድ ማጠናቀር፣ ፕሮ እትም |